J'avais essayé le framework MC-SDK de STM et je n'ai pas du tout été convaincu dans notre usage de volant à FFB.

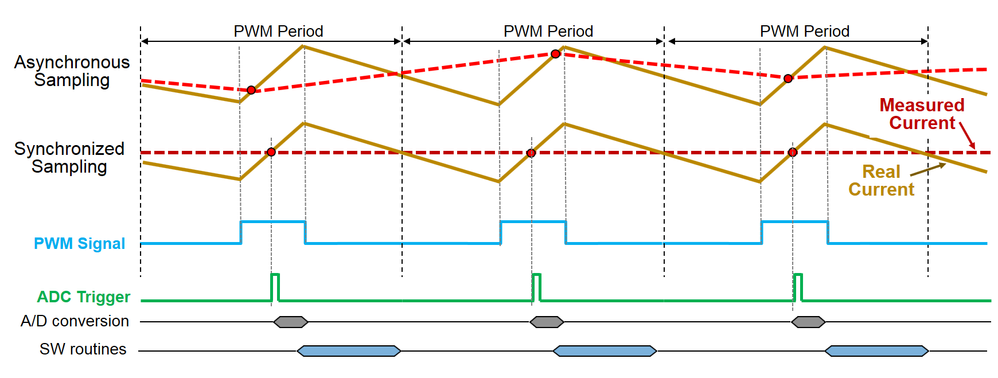

La pauvreté de l'algo faisait que le moteur était très bruité, la fréquence de controle du PWM trop basse.

C'était il y a un poil plus de 2 ans, les choses ont peut etre évoluées.

J'ai passé un peu de temps à regarder, je trouve le code très lisible. L'algo est un algo FOC tout ce qu'il y a de plus classique, je doute que ce soit lui qui amène le bruit. Tout est réglable, y compris la fréquence PWM. Dans les docs et sur d'autres forums j'ai vu passer des captures qui étaient très propres.

Je serai fixé quand j'aurai testé.